# CLOCK AND CONTROL BOARD FOR THE CSC EMU PERIPHERAL AND TRACK FINDER ELECTRONICS

### **CCB2004** Specification (Production Board)

Rice University

Version 3.4

06/27/2007

#### **Abstract**

This document describes the functionality of the production version of the Clock and Control Board (CCB2004) for the CMS EMU peripheral electronics and its communication with other modules in the peripheral crate. This CCB2004 can also be used in the CSC Track Finder crate.

#### Introduction

The CSC EMU electronics includes chamber-mounted Front End Boards (FEB), connected to electronics on the periphery of the detector. The peripheral Trigger/DAQ electronics resides in VME 9U crates and includes: the combined Cathode LCT/Trigger Motherboard cards (TMB), the Data Acquisition Motherboard (DAQMB), the Muon Port Card (MPC) and the Clock and Control Board (CCB). More details about the peripheral backplane and communications between modules are given in [1].

All elements of the EMU electronics will be synchronized with the LHC bunch crossing frequency. The Timing, Trigger and Control (TTC) system, which is used for this purpose for all LHC detectors, has been specified and a detailed description of this system and its functionality can be found, for example, in [2-3]. The TTC system is based on an optical fan-out system and provides for the distribution of the LHC timing reference signal, the first level trigger decisions and control commands to about 1000 destinations. At the lowest level of the TTC system, the TTCrx ASIC [3] receives the control and synchronization data from the central TTC system through the optical cable and outputs TTL-compatible TTC signals in parallel form. The TTCrx is mounted on a small mezzanine card that is designed at CERN and installed on the main Clock and Control Board.

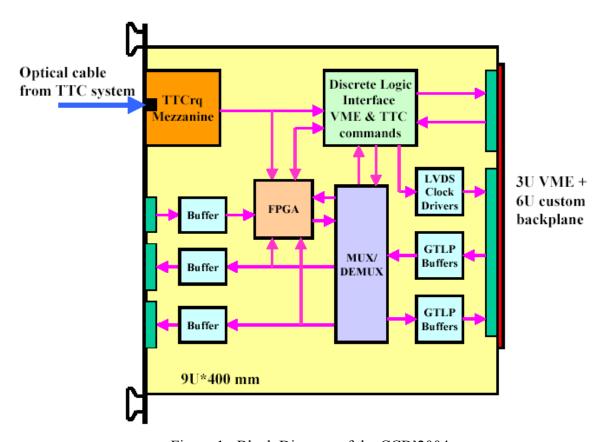

Block diagram of the CCB2004 is shown on Figure 1. There are several new features added into design as compared to the previous version which we will refer to as CCB'2001 [4]. The new CCB2004 board can accommodate not only the TTCrm [3] mezzanine with the TTCrx ASIC, but also the most recent version of the TTC mezzanine card, the TTCrq [5], that has an additional 26-pin connector and provides low-jitter clock outputs of 40Mhz, 80Mhz and 160MHz. The CCB2004 may decode several commands

not only from the broadcast lines Brcst[7..2] as the CCB2001, but also from the Data[7..0] bus that is used for the individually addressed commands.

The CCB2001 functionality was implemented using a mezzanine mounted Altera EPF10K100A PLD. In order to reduce the cost, improve radiation tolerance and decrease the reconfiguration time we decided to use a Xilinx Virtex-2 FPGA mounted directly on the main CCB2004 board. The most critical part of the CCB2004 functionality is implemented in discrete CMOS logic that is immune to single-event upsets (SEU) at the expected dosage. These functions include the VME address and command decoding, generation of Hard\_reset commands, clock and command distribution to custom backplane. An FPGA may experience SEU's however, and in order to prevent malfunctioning, it can be reloaded from its EPROM upon common or CCB-specific Hard reset command.

Another new feature is the ability to distribute an 80Mhz clock from the TTRrq to the Muon Port Card over dedicated LVDS lines. This low jitter clock can be used to drive the gigabit serializers residing on the MPC board.

Estimated power consumption: +3.3V - < 2 A, +5V - < 1 A.

Figure 1: Block Diagram of the CCB'2004

#### 1. Modes of Operations

The most critical functions of the CCB2004 are implemented in discrete logic. Among these functions are the following:

- VME A24D16 slave interface;

- translation of all basic signals from the TTCrq mezzanine to custom backplane;

- decoding of Hard\_reset commands from Brcst[7..2] and Data[7..2] lines and generation of 500 ns Hard\_Reset pulses to custom backplane;

- access to TTCrq board over I2C serial bus under VME control;

- JTAG access to FPGA/EPROM from VME;

- monitoring of the Conf\_Done signals from all connected peripheral or TF boards.

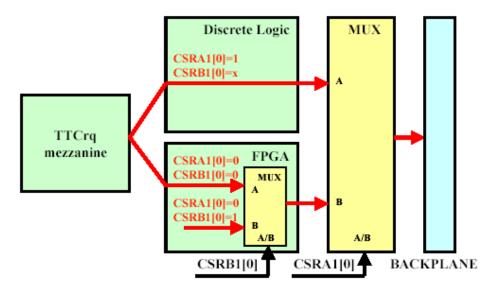

The FPGA can accept all the signals from the TTCrq board, and can generate all the backplane signals to peripheral boards, providing more flexibility than the discrete logic. The choice of interface between the TTCrq mezzanine and custom backplane (discrete logic or FPGA) is defined by CSRA1[0] which is implemented in a discrete logic (Fig.2). When CSRA1[0]=1, the interface is a discrete logic interface ("discrete logic" mode). When CSRA1[0]=0, the interface is an FPGA ("FPGA" mode). In "FPGA" mode two options are possible: when TTC commands are coming from the TTCrq (if CSRB1[0]=0) and when they are generated upon write into CSRB2 and CSRB3 (if CSRB1[0]=1). Also, independently from CSRB1[0], several commands (see Table 8, starting from Base+50 address) can be generated upon VME write to dedicated addresses. This option provides compatibility with the CCB'2001 board.

Figure 2: Modes of Operation

After power cycling and reloading from EPROM all the registers inside the FPGA are set to "0". This means all sources of L1ACC are enabled and the CCB'2004 will not hold the next L1ACC and Pretriggers after the first L1ACC has been sent to custom backplane.

### 2. TTC Interface and TTCrq Mezzanine Board

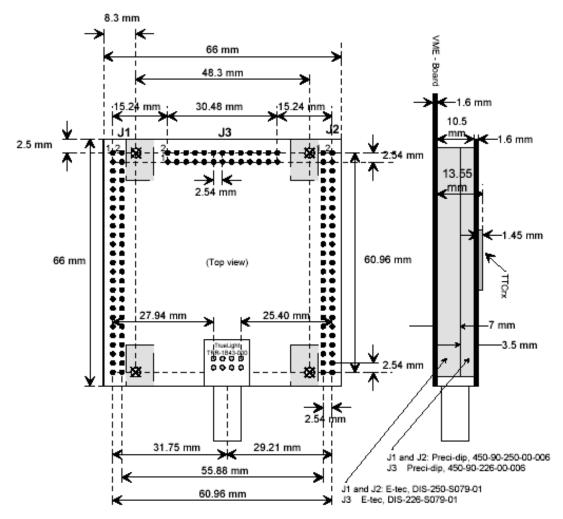

The list of signals that the CCB2004 accepts and transmits from/to the TTC mezzanine board is given in Table 1. Pin assignment of three mezzanine connectors is shown in Table 2. The board dimensions are given on Figure 2.

Table 1: Interface signals to/from TTC mezzanine card

| Signal           | Bits     | Short Description                                                            |

|------------------|----------|------------------------------------------------------------------------------|

|                  |          |                                                                              |

| BCntRes          |          | 50-pin connectors backward compatible with TTCrm mezzanine card              |

|                  | 1        | Bunch Counter Reset signal                                                   |

| BCntStr          | 1        | Bunch Counter Strobe. Indicates that a bunch number is present on the output |

| D                | (        | BCnt<11:0> bus                                                               |

| Brcst<7:2>       | 6        | Broadcast commands/data output bus                                           |

| BrcstStr<2:1>    | 2        | Broadcast messages strobes                                                   |

| Clock40Des1      | 1        | LHC 40.08 MHz deskewed reference clock signal                                |

| DbErStr          | 1        | Indicates that a double error or a frame error has occurred                  |

| Dout<7:0>        | 8        | Data bus. Normally used to output the data content of an individually-       |

|                  |          | addressed commands/data                                                      |

| DQ<3:0>          | 4        | Data qualifier bits. Indicate the type of data on the data bus register      |

| BCnt<110>        | 12       | Bunch or Event counter outputs                                               |

| DoutStr          | 1        | Data out strobe. Indicates valid data on the data bus                        |

| EvCntHStr        | 1        | Event counter high word strobe                                               |

| EvCntLStr        | 1        | Event counter low word strobe                                                |

| EvCntRes         | 1        | Event counter reset signal                                                   |

| L1Accept         | 1        | First level trigger accept signal                                            |

| Reset b          | 1        | Reset TTCrx ASIC, active "low"                                               |

| SinErrStr        | 1        | Single error strobe                                                          |

| SubAddr<7:0>     | 8        | Subaddress bus. Used to output the subaddress content of an individually     |

|                  |          | address commands/data                                                        |

| TTCReady         | 1        | Indicates that TTCrx ASIC is ready for normal operation                      |

| SDA              | 1        | Data Line of I2C interface                                                   |

| SCL              | 1        | Clock Line of I2C interface                                                  |

| Total            | 54       |                                                                              |

| Sign             | als to/f | rom an additional 26-pin connector (TTCrq mezzanine only)                    |

| FoSelect<30>     | 4        | Control inputs for the VCXO free running oscillation frequency (QPLL only)   |

| Mode             | 1        | QPLL multiplication mode control input                                       |

| Restart          | 1        | Enable/disable automatic restart of the PLL (control input for the QPLL)     |

| ExternalControl  | 1        | Control input for the VCXO (QPLL only)                                       |

| Locked           | 1        | QPLL output status signal                                                    |

| 40Mhz clock      | 2        | LVDS clock outputs                                                           |

| 80/60Mhz clock   | 2        | LVDS clock outputs                                                           |

| 160/120Mhz clock | 2        | LVDS clock outputs                                                           |

| 40Mhz CMOS       | 1        | CMOS 40Mhz clock output                                                      |

| ~Reset           | 1        | QPLL control input, active "low"                                             |

| Error            | 1        | QPLL status output                                                           |

| Total            | 17       | 1                                                                            |

|                  |          |                                                                              |

The QPLL ASIC residing on the TTCrq mezzanine card has several control inputs that are connected to the FPGA. All control inputs are set into default states using on-board pull-up and pull-down resistors.

Table 2: Pin assignment of the TTCmr/TTCrq mezzanine connectors

|     |                   | 1 111 40018 |     | Commenter 12  | 1 01 4 1110 |     |                       | 1      |

|-----|-------------------|-------------|-----|---------------|-------------|-----|-----------------------|--------|

| D:  | Connector J1      | Т           | D:  | Connector J2  | Т           |     | onnector J3 (TTC)     |        |

| Pin | Signal<br>Clock40 | Type        | Pin | Signal        | Type        | Pin | Signal<br>F0Select<0> | Type   |

| 1   |                   | Output      | 1   | BrestStr2     | Output      | 1   |                       | Input  |

| 3   | Clock40Des1       | Output      | 3   | ClockL1Accept | Output      | 3   | Mode                  | Input  |

| 4   | Brest<5>          | Output      | 4   | Brest<6>      | Output      | 4   | InLVDS+               | Input  |

|     | Brest<4>          | Output      | 5   | Brest<7>      | Output      |     | InLVDS-               | Input  |

| 5   | Brest<3>          | Output      |     | EvCntRes      | Output      | 5   | GND                   | Power  |

| 6   | Brest<2>          | Output      | 6   | L1Accept      | Output      | 6   | ExternalClock         | Input  |

| 7   | Clock40Des2       | Output      | 7   | EvCntLStr     | Output      | 7   | AutoRestart           | Input  |

| 8   | BrestStr1         | Output      | 8   | EvCntHStr     | Output      | 8   | ExternalContr         | Input  |

| 9   | DbErrStr          | Output      | 9   | BentRes       | Output      | 9   | F0Select<3>           | Input  |

| 10  | SinErrStr         | Output      | 10  | GND           | Power       | 10  | ~Reset                | Input  |

| 11  | SubAdd<0>         | Bidir       | 11  | BCnt<0>       | Output      | 11  | Locked                | Output |

| 12  | SubAdd<1>         | Bidir       | 12  | BCnt<1>       | Output      | 12  | Error                 | Output |

| 13  | SubAdd<2>         | Bidir       | 13  | BCnt<2>       | Output      | 13  | GND                   | Power  |

| 14  | SubAdd<3>         | Bidir       | 14  | BCnt<3>       | Output      | 14  | Lvds80Mhz-            | Output |

| 15  | SubAdd<4>         | Bidir       | 15  | BCnt<4>       | Output      | 15  | Lvds80Mhz+            | Output |

| 16  | SubAdd<5>         | Bidir       | 16  | BCnt<5>       | Output      | 16  | GND                   | Power  |

| 17  | SubAdd<6>         | Bidir       | 17  | BCnt<6>       | Output      | 17  | F0Select<2>           | Input  |

| 18  | SubAdd<7>         | Bidir       | 18  | BCnt<7>       | Output      | 18  | GND                   | Power  |

| 19  | DQ<0>             | Output      | 19  | BCnt<8>       | Output      | 19  | Lvds160Mhz+           | Output |

| 20  | DQ<1>             | Output      | 20  | BCnt<9>       | Output      | 20  | Lvds160Mhz-           | Output |

| 21  | DQ<2>             | Output      | 21  | BCnt<10>      | Output      | 21  | GND                   | Power  |

| 22  | DQ<3>             | Output      | 22  | BCnt<11>      | Output      | 22  | Lvds40Mhz-            | Output |

| 23  | DoutStr           | Output      | 23  | JTAGTMS       | Input       | 23  | Lvds40Mhz+            | Output |

| 24  | GND               | Power       | 24  | JTAGTRST_b    | Input       | 24  | F0Select<1>           | Input  |

| 25  | Dout<0>           | Bidir       | 25  | JTAGTCK       | Input       | 25  | Cmos40Mhz             | Output |

| 26  | Dout<1>           | Bidir       | 26  | JTAGTDO       | Output      | 26  | GND                   | Power  |

| 27  | Dout<2>           | Bidir       | 27  | SDA           | Bidir       |     |                       |        |

| 28  | Dout<3>           | Bidir       | 28  | JTAGTDI       | Input       |     |                       |        |

| 29  | Dout<4>           | Bidir       | 29  | BCntStr       | Output      |     |                       |        |

| 30  | Dout<5>           | Bidir       | 30  | Serial_B_Chan | Output      |     |                       |        |

| 31  | Dout<6>           | Bidir       | 31  | GND           | Power       |     |                       |        |

| 32  | Dout<7>           | Bidir       | 32  | GND           | Power       |     |                       |        |

| 33  | Reset_b           | Input       | 33  | GND           | Power       |     |                       |        |

| 34  | TTCReady          | Output      | 34  | GND           | Power       |     |                       |        |

| 35  | GND               | Power       | 35  | +5V           | Power       |     |                       |        |

| 36  | GND               | Power       | 36  | +5V           | Power       |     |                       |        |

| 37  | GND               | Power       | 37  | +5V           | Power       |     |                       |        |

| 38  | GND               | Power       | 38  | +5V           | Power       |     |                       |        |

| 39  | GND               | Power       | 39  | QPLL power    | Passive     |     |                       |        |

| 40  | GND               | Power       | 40  | SCL           | Input       |     |                       |        |

| 41  | GND               | Power       | 41  | GND           | Power       |     |                       |        |

| 42  | GND               | Power       | 42  | GND           | Power       |     |                       |        |

| 43  | GND               | Power       | 43  | +5V           | Power       |     |                       |        |

| 44  | GND               | Power       | 44  | +5V           | Power       |     |                       |        |

| 45  | GND               | Power       | 45  | +5V           | Power       |     |                       |        |

| 46  | GND               | Power       | 46  | +5V           | Power       |     |                       |        |

| 47  | GND               | Power       | 47  | GND           | Power       |     |                       |        |

| 48  | GND               | Power       | 48  | GND           | Power       |     |                       |        |

| 49  | GND               | Power       | 49  | GND           | Power       |     |                       |        |

| 50  | GND               | Power       | 50  | GND           | Power       |     |                       |        |

|     |                   |             |     |               |             |     |                       |        |

Figure 2: TTCrq layout and dimensions

Each TTCrq mezzanine board has a unique 14-bit number that is defined by on-board jumpers. For more details see chapter 8 of the TTCrx Reference Manual [3]. This number can be accessed via I2C bus (see section 6) or from CSRB18 (see section 4.21). The settings on TTCrq mezzanines installed on production CCB2004 boards are the following: SubAdd[7..0]=1 and Data[7..0]=1..255. As a rule, the code on Data[7..0] lines is equal to serial number of the CCB2004 board (marked on the front panel and on the top side of the main board). The other jumpers on TTCrq mezzanine described in [5] are:

- R53..R55 (termination resistors for 40/80/160Mhz LVDS clock outputs) are not installed (there are 100 Ohm termination resistors R15..R17 installed on CCB2004)

- ST19 is set to "TTCrx" clock source for clock pin 2 on J1 connector

- R59 is not mounted (on-board regulator provides the QPLL power)

### 2. Custom Backplane Interface

The lists of signals that the CCB2004 distributes to the custom peripheral and Track Finder backplanes are given in Tables 3A and 3B respectively. Pin assignment of the

custom peripheral backplane connectors is based on [6] (both on-board connectors are AMP 100145-1 female 125-pin 25-row by 5 pins) and given in Tables 4A and 5A. The CCB2004 may also be used in the CSC Track Finder crate with another custom backplane [7]. In this case the CCB2004 distributes/receives a subset of signals described in Tables 4B and 5B.

Texas Instruments SN74GTLPH16912GR transceivers are used for the communication with other modules in a crate. All GTLP backplane signals are sent in "negative" logic as proposed in [1], i.e. active output signal corresponds to a "low" GTLP level. The same is expected for all incoming backplane signals. 28 point-to-point cfg\_done signals (from TMB, DMB and MPC) are terminated on CCB2004 board with 56 Ohm resistors to +1.5V. All bussed signals are terminated on both ends of the backplane.

Table 3A: Peripheral Backplane Interface Signals

|                                          | Tat  | ole 3A: Peripheral E    | sackplane inter   | lace Signais   |       |                |

|------------------------------------------|------|-------------------------|-------------------|----------------|-------|----------------|

| Signal                                   | Bits | Source                  | Destination       | Туре           | Logic | Duration/Level |

|                                          |      | Clock Bus: Clock Dis    | tribution & Bunch | Crossing       |       |                |

| ccb_clock40                              | 19   | TTCrx, QPLL, osc        | All 19 Slots      | Point-to-point | LVDS  | 40.08MHz       |

| Clk80_MPC                                | 1    | QPLL, oscillator        | MPC               | Point-to-point | LVDS  | 80.16MHz       |

|                                          |      | Fast C                  | Control Bus       |                |       |                |

| ccb_clock40_enable                       | 1    | TTCrx, QPLL, oscillator | All 19 Slots      | Bussed         | GTLP  | 40.08Mhz       |

| ccb_cmd[50]                              | 6    | TTCrx                   | All 19 Slots      | Bussed         | GTLP  | Level          |

| Ccb_ttcrx_ready (former ccb_reserved[0]) | 1    | TTCrx                   | All 19 slots      | Bussed         | GTLP  | Level          |

| QPLL_locked (former ccb_reserved[1]      | 1    | QPLL ASIC               | All 19 Slots      | Bussed         | GTLP  | Level          |

| ccb_evcntres                             | 1    | TTCrx                   | All 19 Slots      | Bussed         | GTLP  | 25 ns          |

| ccb_bcntres                              | 1    | TTCrx                   | All 19 Slots      | Bussed         | GTLP  | 25 ns          |

| Ccb_L1Reset (former ccb_reserved[4])     | 1    | DTTCrx                  | All 19 Slots      | Bussed         | GTLP  | 25 ns          |

| ccb cmd strobe                           | 1    | TTCrx                   | All 19 Slots      | Bussed         | GTLP  | 25 ns          |

| ccb_bx0                                  | 1    | DTTCrx                  | All 19 Slots      | Bussed         | GTLP  | 25 ns          |

| ccb_l1accept                             | 1    | TTCrx                   | All 19 Slots      | Bussed         | GTLP  | 25 ns          |

| ccb_data[70]                             | 8    | TTCrx                   | All 19 Slots      | Bussed         | GTLP  | Level          |

| ccb_data_strobe                          | 1    | TTCrx                   | All 19 Slots      | Bussed         | GTLP  | 25 ns          |

| ccb_reserved[32]                         | 2    | VME                     | All 19 Slots      | Bussed         | GTLP  | Level          |

| Total                                    | 26   |                         |                   |                |       |                |

|                                          | T    | MB Reload Bus: ALC      | Γ+CLCT+TMB FI     | PGA Reload     |       |                |

| tmb_hard_reset                           | 1    | DTTCrx (*)              | 9 TMB             | Bussed         | GTLP  | 400 ns         |

| tmb_cfg_done[80]                         | 9    | 9 TMB                   | VME               | Point-to-Point | GTLP  | Level          |

| alct_hard_reset                          | 1    | DTTCrx (*)              | 9 TMB             | Bussed         | GTLP  | 400 ns         |

| alct_cfg_done[80]                        | 9    | 9 TMB (from<br>ALCT)    | VME               | Point-to-Point | GTLP  | Level          |

| Tmb_soft_reset (former tmb_reserved[1])  | 1    | VME                     | 9 TMB             | Bussed         | GTLP  | Level          |

| tmb_reserved[0]                          | 1    | VME                     | 9 TMB             | Bussed         | GTLP  | Level          |

| Total                                    | 22   |                         |                   |                |       |                |

|                                         |    | MPC Reload Bus        | s: MPC FPGA Re    | load           |      |        |

|-----------------------------------------|----|-----------------------|-------------------|----------------|------|--------|

| mpc_hard_reset                          | 1  | DTTCrx (*)            | MPC               | Point-to-Point | GTLP | 400 ns |

| mpc cfg done                            | 1  | MPC                   | CCB               | Point-to-Point | GTLP | Level  |

| Mpc_soft_reset (former mpc_reserved[2]) | 1  | VME                   | MPC               | Point-to-Point | GTLP | Level  |

| mpc_reserved[10]                        | 2  | VME                   | MPC               | Point-to-Point | GTLP | Level  |

| Total                                   | 5  |                       |                   |                |      |        |

|                                         |    | DMB Reload Bus        | s: DMB FPGA Re    | load           |      |        |

| dmb_hard_reset                          | 1  | DTTCrx (*)            | 9 DMB             | Bussed         | GTLP | 400 ns |

| dmb_cfg_done[80]                        | 9  | 9 DMB                 | CCB               | Point-to-Point | GTLP | Level  |

| Dmb_soft_reset (former                  | 1  | VME                   | 9 DMB             | Bussed         | GTLP | Level  |

| dmb_reserved[2])                        |    |                       |                   |                |      |        |

| dmb_reserved[10]                        | 2  | VME                   | 9 DMB             | Bussed         | GTLP | Level  |

| Total                                   | 13 |                       |                   |                |      |        |

|                                         | Γ  | OAQ Special Purpose B | bus [Used by DMB  | and TMB]       |      |        |

| dmb_cfeb_calibrate[20]                  | 3  | VME                   | 9 DMB 9TMB        | Bussed         | GTLP | Level  |

| dmb_l1a_release                         | 1  | 9 DMB, 9 TMB          | VME               | Bussed         | GTLP | Level  |

| dmb_reserved_out[40]                    | 5  | VME                   | 9 DMB 9TMB        | Bussed         | GTLP | Level  |

| dmb_reserved_in[20]                     | 3  | 9 DMB, 9 TMB          | VME               | Bussed         | GTLP | Level  |

| Total                                   | 12 |                       |                   |                |      |        |

|                                         |    | Trigger Special Purpo | se Bus [Used by T | MB only]       |      |        |

| alct adb pulse sync                     | 1  | VME                   | 9 TMB             | Bussed         | GTLP | Level  |

| alct adb pulse async                    | 1  | VME                   | 9 TMB             | Bussed         | GTLP | Level  |

| clct_external_trigger                   | 1  | VME                   | 9 TMB             | Bussed         | GTLP | Level  |

| alct_external_trigger                   | 1  | VME                   | 9 TMB             | Bussed         | GTLP | Level  |

| clct_status[80]                         | 9  | 9 TMB                 | FP                | Bussed         | GTLP | Level  |

| alct_status[80]                         | 9  | 9 TMB                 | FP                | Bussed         | GTLP | Level  |

| tmb_l1a_request                         | 1  | 9 TMB                 | VME               | Bussed         | GTLP | Level  |

| tmb_l1a_release                         | 1  | 9 TMB                 | VME               | Bussed         | GTLP | Level  |

| tmb_reserved_in[40]                     | 5  | 9 TMB                 | VME               | Bussed         | GTLP | Level  |

| tmb_reserved_out[20]                    | 3  | VME                   | 9 TMB             | Bussed         | GTLP | Level  |

| Total                                   | 32 |                       |                   |                |      |        |

<sup>(\*) –</sup> decoded from Brcst[7..2] or Data[7..2]

Table 3B: Track Finder Backplane Interface Signals

|                                          | 1 4010 | 3B. Track Finder        | Dackplane Into     | criace Signais           |              |                                             |

|------------------------------------------|--------|-------------------------|--------------------|--------------------------|--------------|---------------------------------------------|

| Signal                                   | Bits   | Source                  | Destination        | Туре                     | Logic        | Duration/Level                              |

|                                          |        | Clock Bus: Clock Dis    | tribution & Bunch  | Crossing                 |              |                                             |

| ccb_clock40                              | 17     | TTCrx, QPLL, oscillator | All 17 Slots       | Point-to-point           | LVDS         | 40.08MHz or<br>80.16Mhz, see<br>section 2.1 |

| Clk80 MPC                                | 3      | QPLL, oscillator        | 3 MPC              | Point-to-point           | LVDS         | 80.16MHz                                    |

|                                          |        | Fast (                  | Control Bus        |                          |              |                                             |

| ccb_clock40_enable                       | 1      | TTCrx, QPLL, oscillator | All 17 Slots       | Bussed                   | GTLP         | 40.08Mhz                                    |

| ccb_cmd[50]                              | 6      | TTCrx                   | All 17 Slots       | Bussed                   | GTLP         | Level                                       |

| Ccb_ttcrx_ready (former ccb_reserved[0]) | 1      | TTCrx                   | All 17 slots       | Bussed                   | GTLP         | Level                                       |

| QPLL_locked (former ccb_reserved[1]      | 1      | QPLL ASIC               | All 17 Slots       | Bussed                   | GTLP         | Level                                       |

| ccb_evcntres                             | 1      | TTCrx                   | All 17 Slots       | Bussed                   | GTLP         | 25 ns                                       |

| ccb_bcntres                              | 1      | TTCrx                   | All 17 Slots       | Bussed                   | GTLP         | 25 ns                                       |

| Ccb_L1Reset (former ccb_reserved[4])     | 1      | DTTCrx                  | All 17 Slots       | Bussed                   | GTLP         | 25 ns                                       |

| ccb_cmd_strobe                           | 1      | TTCrx                   | All 17 Slots       | Bussed                   | GTLP         | 25 ns                                       |

| ccb_bx0                                  | 1      | DTTCrx                  | All 17 Slots       | Bussed                   | GTLP         | 25 ns                                       |

| ccb_l1accept                             | 1      | TTCrx                   | All 17 Slots       | Bussed                   | GTLP         | 25 ns                                       |

| ccb_data[70]                             | 8      | TTCrx                   | All 17 Slots       | Bussed                   | GTLP         | Level                                       |

| ccb_data_strobe                          | 1      | TTCrx                   | All 17 Slots       | Bussed                   | GTLP         | 25 ns                                       |

| ccb_reserved[32]                         | 2      | VME                     | All 17 Slots       | Bussed                   | GTLP         | Level                                       |

| Total                                    | 26     |                         |                    |                          |              |                                             |

|                                          |        | SP, MS, MPC             | C, DDU Reload Bu   | IS                       |              |                                             |

| sp_hard_reset                            | 1      | DTTCrx (*)              | 12 SP              | Bussed                   | GTLP         | 400 ns                                      |

| sp_cfg_done[121]                         | 12     | 12 SP                   | VME                | Point-to-Point           | GTLP         | Level                                       |

| ms_hard_reset                            | 1      | DTTCrx (*)              | MS                 | Point-to-Point           | GTLP         | 400 ns                                      |

| ms_cfg_done                              | 1      | MS                      | VME                | Point-to-Point           | GTLP         | Level                                       |

| mpc_hard_reset                           | 1      | DTTCtx(*)               | 3 MPC              | Bussed                   | GTLP         | 400 ns                                      |

| mpc_cfg_done                             | 3      | 3 MPC                   | VME                | Point-to-Point           | GTLP         | Level                                       |

| ddu_cfg_done Total                       | 1 20   | DDU                     | VME                | Point-to-Point           | GTLP         | Level                                       |

| Total                                    | 20     | C                       |                    |                          |              |                                             |

| 14                                       |        |                         | e and Reserved Lin | •                        | amr n        | T = 1                                       |

| sp_lla_request                           | 1      | 12 SP                   | VME                | Bussed                   | GTLP         | Pulse                                       |

| ms_l1a_request                           | 1      | MS                      | VME                | Point-to-Point           | GTLP         | Pulse                                       |

| ms_to_ccb[10]                            | 2      | MS<br>12 SP             | VME                | Point-to-Point           | GTLP         |                                             |

| sp_to-ccb[20]                            | 3 4    | 12 SP<br>CCB            | VME<br>MS          | Bussed<br>Point-to-Point | GTLP<br>GTLP |                                             |

| ccb_to_ms[30] Total                      | 11     | ССВ                     | IVIS               | romit-to-romi            | GILP         |                                             |

| 1 Otal                                   | 11     |                         |                    |                          |              |                                             |

<sup>(\*) –</sup> decoded from Brest[7..2] or Data[7..2]

|     |              | Table 4 | A: X40 Backpla  | ne Con | nector, Pe | eriphera | al Crate     |     |              |

|-----|--------------|---------|-----------------|--------|------------|----------|--------------|-----|--------------|

| Pin | Signal       | Pin     | Signal          | Pin    | Signal     | Pin      | Signal       | Pin | Signal       |

| A1  | CLK+DMB1     | B1      | CLK-DMB1        | C1     | GND        | D1       | CLK+TMB1     | E1  | CLK-TMB1     |

| A2  | CLK+TMB2     | B2      | CLK-TMB2        | C2     | GND        | D2       | CLK+DMB9     | E2  | CLK-DMB9     |

| A3  | CLK+DMB2     | В3      | CLK-DMB2        | C3     | GND        | D3       | CLK+TMB9     | E3  | CLK-TMB9     |

| A4  | CLK+TMB3     | B4      | CLK-TMB3        | C4     | GND        | D4       | CLK+DMB8     | E4  | CLK-DMB8     |

| A5  | CLK+DMB3     | В5      | CLK-DMB3        | C5     | GND        | D5       | CLK+TMB8     | E5  | CLK-TMB8     |

| A6  | CLK+TMB4     | В6      | CLK-TMB4        | C6     | GND        | D6       | CLK+DMB7     | E6  | CLK-DMB7     |

| A7  | CLK+DMB4     | В7      | CLK-DMB4        | C7     | GND        | D7       | CLK+TMB7     | E7  | CLK-TMB7     |

| A8  | CLK+TMB5     | В8      | CLK-TMB5        | C8     | GND        | D8       | CLK+DMB6     | E8  | CLK-DMB6     |

| A9  | CLK+DMB5     | В9      | CLK-DMB5        | C9     | GND        | D9       | CLK+TMB6     | E9  | CLK-TMB6     |

| A10 | CLK+MPC      | B10     | CLK-MPC         | C10    | GND        | D10      | alct cfg d 9 | E10 | dmb cfg d 9  |

| A11 | tmb_cfg_d_1  | B11     | alct_cfg_d_1    | C11    | GND        | D11      | dmb_cfg_d_8  | E11 | tmb_cfg_d_9  |

| A12 | dmb cfg d 1  | B12     | tmb_cfg_d_2     | C12    | GND        | D12      | tmb cfg d 8  | E12 | alct cfg d 8 |

| A13 | alct cfg d 2 | B13     | dmb_cfg_d_2     | C13    | GND        | D13      | alct_cfg_d_7 | E13 | dmb_cfg_d_7  |

| A14 | tmb cfg d 3  | B14     | alct_cfg_d_3    | C14    | GND        | D14      | dmb_cfg_d_6  | E14 | tmb_cfg_d_7  |

| A15 | dmb cfg d 3  | B15     | tmb cfg d 4     | C15    | GND        | D15      | tmb cfg d 6  | E15 | alct_cfg_d_6 |

| A16 | alct cfg d 4 | B16     | dmb_cfg_d_4     | C16    | GND        | D16      | Mpc h reset  | E16 | Mpc rsv0     |

| A17 | Tmb_cfg_d_5  | B17     | alct_cfg_d_5    | C17    | GND        | D17      | Mpc rsv1     | E17 | Mpc softres  |

| A18 | dmb cfg d 5  | B18     |                 | C18    | GND        | D18      | mpc_c_done   | E18 | · -          |

| A19 | Clock enable | B19     | Ccb rsv4        | C19    | GND        | D19      | Clk80+MPC    | E19 | Clk80-MPC    |

| A20 | Ccb cmd0     | B20     | Ccb cmd1        | C20    | GND        | D20      | Ccb cmd2     | E20 | Ccb cmd3     |

| A21 | Ccb cmd4     | B21     | Ccb cmd5        | C21    | GND        | D21      | Ccb eventres | E21 | Ccb bentres  |

| A22 | Ccb cmd str  | B22     | Ccb bx0         | C22    | GND        | D22      | Ccb_l1accept | E22 | Ccb data st  |

| A23 | Ccb data0    | B23     | Ccb data1       | C23    | GND        | D23      | Ccb data2    | E23 | Ccb data3    |

| A24 | Ccb data4    | B24     | Ccb data5       | C24    | GND        | D24      | Ccb data6    | E24 | Ccb data7    |

| A25 | Ccb rsv0     | B25     | Ccb rsv1        | C25    | GND        | D25      | Ccb rsv2     | E25 | Ccb rsv3     |

|     |              |         | 3: X40 Backplan |        | ector, Tra |          | ler Crate    |     |              |

| Pin | Signal       | Pin     | Signal          | Pin    | Signal     | Pin      | Signal       | Pin | Signal       |

| A1  | CLK+DDU      | B1      | CLK-DDU         | C1     | GND        | D1       |              | E1  |              |

| A2  | CLK+MPC1     | B2      | CLK-MPC1        | C2     | GND        | D2       |              | E2  |              |

| A3  | CLK+MPC2     | В3      | CLK-MPC2        | C3     | GND        | D3       | CLK+SP12     | E3  | CLK-SP12     |

| A4  | CLK+MPC3     | B4      | CLK-MPC3        | C4     | GND        | D4       | CLK+SP11     | E4  | CLK-SP11     |

| A5  | CLK+SP1      | B5      | CLK-SP1         | C5     | GND        | D5       | CLK+SP10     | E5  | CLK-SP10     |

| A6  | CLK+SP2      | В6      | CLK-SP2         | C6     | GND        | D6       | CLK+SP9      | E6  | CLK-SP9      |

| A7  | CLK+SP3      | В7      | CLK-SP3         | C7     | GND        | D7       | CLK+SP8      | E7  | CLK-SP8      |

| A8  | CLK+SP4      | В8      | CLK-SP4         | C8     | GND        | D8       | CLK+SP7      | E8  | CLK-SP7      |

| A9  | CLK+SP5      | В9      | CLK-SP5         | C9     | GND        | D9       | CLK+MS       | E9  | CLK-MS       |

| A10 | CLK+SP6      | B10     | CLK-SP6         | C10    | GND        | D10      |              | E10 | sp_c_don_12  |

| A11 |              | B11     |                 | C11    | GND        | D11      |              | E11 | sp_c_don_11  |

| A12 |              | B12     |                 | C12    | GND        | D12      |              | E12 | sp_c_don_10  |

| A13 | ddu_cfg_done | B13     | mpc_c_don_1     | C13    | GND        | D13      |              | E13 | sp_c_done_9  |

| A14 | mpc_c_done_2 | B14     | mpc_c_don_3     | C14    | GND        | D14      |              | E14 | sp_c_done_8  |

| A15 | sp_c_done_1  | B15     | sp_c_done_2     | C15    | GND        | D15      |              | E15 | sp_c_done_7  |

| A16 | sp_c_done_3  | B16     | sp_c_done_4     | C16    | GND        | D16      |              | E16 |              |

| 1   | i            | D 1 =   |                 |        | CNID       | D 15     |              | D15 |              |

D17

D18

D19

D20

D21

D22

D23

D24

D25

ms c done

Ccb\_cmd2

Ccb\_evcntres

Ccb 11accept

Ccb\_data2

Ccb data6

Ccb\_rsv2

**GND**

**GND**

**GND**

**GND**

**GND**

**GND**

GND

GND

GND

A17

A18

A19

A20

A21

A22

A23

A24

A25

sp\_c\_done\_5

Clock\_enable

Ccb\_cmd0

Ccb cmd4

Ccb cmd str

Ccb\_data0

Ccb\_data4

Ccb\_rsv0

B17

B18

B19

B20

B21

B22

B23

B24

B25

sp\_c\_done\_6

Ccb\_rsv4

Ccb\_cmd1

Ccb cmd5

Ccb bx0

Ccb\_data1

Ccb data5

Ccb\_rsv1

C17

C18

C19

C20

C21

C22

C23

C24

C25

E17

E18

E19

E20

E21

E22

E23

E24

E25

Ccb\_cmd3

Ccb\_bcntres

Ccb data st

Ccb\_data3

Ccb\_data7

Ccb\_rsv3

Table 5A: X41 Backplane Connector, Peripheral Crate

| Pin | Signal       | Pin | Signal       | Pin | Signal | Pin | Signal        | Pin | Signal        |

|-----|--------------|-----|--------------|-----|--------|-----|---------------|-----|---------------|

| A1  | Tmb_h_reset  | B1  | Alct_h_reset | C1  | GND    | D1  | tmb_rsv_0     | E1  | tmb_softres   |

| A2  | Alct_adb_p_s | B2  | alct_adb_p_a | C2  | GND    | D2  | clct_ext_trig | E2  | alct_ext_trig |

| A3  | Clct_status0 | В3  | Clct_status1 | C3  | GND    | D3  | Clct_status2  | E3  | Clct_status3  |

| A4  | Clct_status4 | B4  | Clct_status5 | C4  | GND    | D4  | Clct_status6  | E4  | Clct_status7  |

| A5  | Clct_status8 | B5  | Alct_status0 | C5  | GND    | D5  | alct_status1  | E5  | alct_status2  |

| A6  | Alct_status3 | В6  | Alct_status4 | C6  | GND    | D6  | Alct_status5  | E6  | Alct_status6  |

| A7  | Alct_status7 | В7  | alct_status8 | C7  | GND    | D7  | tmb_l1a_req   | E7  | tmb_l1a_rel   |

| A8  | Tmb_rsv_in0  | В8  | Tmb_rsv_in1  | C8  | GND    | D8  | Tmb_rsv_in2   | E8  | Tmb_rsv_in3   |

| A9  | Tmb_rsv_in4  | В9  | tmb_rsv_o0   | C9  | GND    | D9  | Tmb_rsv_o1    | E9  | Tmb_rsv_o2    |

| A10 | dmb_h_reset  | B10 | dmb_rsv_0    | C10 | GND    | D10 | dmb_rsv_1     | E10 | dmb_softres   |

| A11 | dmb_cfeb_c0  | B11 | dmb_cfeb_c1  | C11 | GND    | D11 | dmb_cfeb_c2   | E11 | dmb_l1a_rel   |

| A12 | dmb_rsv_o0   | B12 | dmb_rsv_o1   | C12 | GND    | D12 | dmb_rsv_o2    | E12 | dmb_rsv_o3    |

| A13 | dmb_rsv_o4   | B13 | dmb_rsv_in0  | C13 | GND    | D13 | dmb_rsv_in1   | E13 |               |

| A14 |              | B14 |              | C14 | +1.5V  | D14 |               | E14 |               |

| A15 |              | B15 |              | C15 | GND    | D15 |               | E15 |               |

| A16 |              | B16 |              | C16 | +1.5V  | D16 |               | E16 |               |

| A17 |              | B17 |              | C17 | GND    | D17 |               | E17 |               |

| A18 |              | B18 |              | C18 | +1.5V  | D18 |               | E18 |               |

| A19 |              | B19 |              | C19 | GND    | D19 |               | E19 |               |

| A20 |              | B20 |              | C20 | +1.5V  | D20 |               | E20 |               |

| A21 |              | B21 |              | C21 | GND    | D21 |               | E21 |               |

| A22 |              | B22 |              | C22 | +1.5V  | D22 |               | E22 |               |

| A23 |              | B23 |              | C23 | GND    | D23 |               | E23 |               |

| A24 |              | B24 |              | C24 | +1.5V  | D24 |               | E24 |               |

| A25 |              | B25 |              | C25 | GND    | D25 |               | E25 |               |

Table 5B: X41 Backplane Connector, Track Finder Crate

| Pin | Signal        | Pin | Signal      | Pin | Signal | Pin | Signal      | Pin | Signal      |

|-----|---------------|-----|-------------|-----|--------|-----|-------------|-----|-------------|

| A1  | sp_hard_reset | B1  | ms_h_reset  | C1  | GND    | D1  |             | E1  |             |

| A2  |               | B2  |             | C2  | GND    | D2  |             | E2  |             |

| A3  |               | В3  |             | C3  | GND    | D3  |             | E3  |             |

| A4  |               | B4  |             | C4  | GND    | D4  |             | E4  |             |

| A5  |               | B5  |             | C5  | GND    | D5  |             | E5  |             |

| A6  |               | В6  |             | C6  | GND    | D6  |             | E6  |             |

| A7  |               | В7  |             | C7  | GND    | D7  | sp_l1a_req  | E7  | ms_l1a_req  |

| A8  | ms_to_ccb_0   | В8  | ms_to_ccb_1 | C8  | GND    | D8  |             | E8  |             |

| A9  |               | В9  |             | C9  | GND    | D9  |             | E9  |             |

| A10 | mpc_h_reset   | B10 |             | C10 | GND    | D10 |             | E10 |             |

| A11 |               | B11 |             | C11 | GND    | D11 |             | E11 |             |

| A12 | ccb_to_ms_0   | B12 | ccb_to_ms_1 | C12 | GND    | D12 | ccb_to_ms_2 | E12 | ccb_to_ms_3 |

| A13 |               | B13 | sp_to_ccb_0 | C13 | GND    | D13 | sp_to_ccb_1 | E13 | sp_to_ccb_2 |

| A14 |               | B14 |             | C14 | +1.5V  | D14 | Clk80+Mpc1  | E14 | Clk80-Mpc1  |

| A15 |               | B15 |             | C15 | GND    | D15 | Clk80+Mpc2  | E15 | Clk80-Mpc2  |

| A16 |               | B16 |             | C16 | +1.5V  | D16 | Clk80+Mpc3  | E16 | Clk80-Mpc3  |

| A17 |               | B17 |             | C17 | GND    | D17 |             | E17 |             |

| A18 |               | B18 |             | C18 | +1.5V  | D18 |             | E18 |             |

| A19 |               | B19 |             | C19 | GND    | D19 |             | E19 |             |

| A20 |               | B20 |             | C20 | +1.5V  | D20 |             | E20 |             |

| A21 |               | B21 |             | C21 | GND    | D21 |             | E21 |             |

| A22 |               | B22 |             | C22 | +1.5V  | D22 |             | E22 |             |

| A23 |               | B23 |             | C23 | GND    | D23 |             | E23 |             |

| A24 |               | B24 |             | C24 | +1.5V  | D24 |             | E24 |             |

| A25 |               | B25 |             | C25 | GND    | D25 |             | E25 |             |

#### 3.1. Clock Distribution

There are four sources of the 40.078Mhz clock on a CCB2004 board: Clock40Des1 from the TTCrx ASIC (1), CMOS40Mhz output from the QPLL ASIC (2), QPLL\_40Mhz after LVDS-to-LVTTL conversion (3) and Clock40Osc (4) that is derived from an on-board oscillator (80.157Mhz divided by 2). One source must be selected using switch S5.

There are two sources of the 80.157Mhz: Clock80Mhz from the QPLL ASIC and Clock80Osc from an on-board oscillator. One source must be selected using switch S7.

All modules in the peripheral crate require a point-to-point 40MHz LVDS clock from the CCB2004. Some modules in the Track Finder crate may require either 40Mhz or 80Mhz clocks over the same lines from the CCB'2004. In order to allow the CCB2004 design to be compatible with both peripheral and Track Finder crates the CCB2004 has a switch that allows to chose 40/80Mhz source for a several slots (see Table 6).

Table 6: Clocking Options in the Peripheral and Track Finder Crates

|      | Table 0. Clock   | ing Options in the r | cripilciai and Track i | maci Ciates    |

|------|------------------|----------------------|------------------------|----------------|

| Slot | Peripheral Crate | Clock Source         | Track Finder Crate     | Clock Source   |

| 1    | Crate Master     | •                    | Crate Master           | -              |

| 2    | TMB1             | 40Mhz                | DDU                    | 40Mhz + 80Mhz  |

| 3    | DMB1             | 40Mhz                | MPC1                   | 40Mhz + 80Mhz  |

| 4    | TMB2             | 40Mhz                | MPC2                   | 40Mhz + 80Mhz  |

| 5    | DMB2             | 40Mhz                | MPC3                   | 40Mhz          |

| 6    | TMB3             | 40Mhz                | SP1                    | 40Mhz or 80Mhz |

| 7    | DMB3             | 40Mhz                | SP2                    | 40Mhz or 80Mhz |

| 8    | TMB4             | 40Mhz                | SP3                    | 40Mhz or 80Mhz |

| 9    | DMB4             | 40Mhz                | SP4                    | 40Mhz or 80Mhz |

| 10   | TMB5             | 40Mhz                | SP5                    | 40Mhz or 80Mhz |

| 11   | DMB5             | 40Mhz                | SP6                    | 40Mhz or 80Mhz |

| 12   | MPC              | 40Mhz + 80Mhz        | CCB                    | TTC/internal   |

| 13   | CCB              | internal             | -                      | -              |

| 14   | TMB6             | 40Mhz                | Muon Sorter            | 40Mhz          |

| 15   | DMB6             | 40Mhz                | -                      | -              |

| 16   | TMB7             | 40Mhz                | SP7                    | 40Mhz or 80Mhz |

| 17   | DMB7             | 40Mhz                | SP8                    | 40Mhz or 80Mhz |

| 18   | TMB8             | 40Mhz                | SP9                    | 40Mhz or 80Mhz |

| 19   | DMB8             | 40Mhz                | SP10                   | 40Mhz or 80Mhz |

| 20   | TMB9             | 40Mhz                | SP11                   | 40Mhz or 80Mhz |

| 21   | DMB9             | 40Mhz                | SP12                   | 40Mhz or 80Mhz |

All clocks are distributed over the peripheral backplane using individual point-to-point LVDS lines. There are fine and coarse delays for the 40Mhz clock and command signals incorporated into TTCrx ASIC. They are programmable via the I2C interface or optical path. In addition to individual clock per each slot there is a common GTLP line (formerly assigned for ccb\_clock\_enable signal) that carries a continuous 40.078Mhz signal selected from one of four sources described above. This signal can be used by Sector Processors in conjunction with the 80Mhz clock.

A dedicated 80Mhz LVDS clock in addition to 40Mhz clock is transmitted to MPC slot in the peripheral crate and to every (out of 3) MPC slot in the Track Finder crate.

#### 3.2. Fast Control and Data Buses

The TTCrx ASIC can distribute broadcast commands over Brcst[7..2] bus and individually addressed commands over Data[7..0] and Subadd[7..0] buses. Six backplane lines ccb\_cmd[5..0] and ccb\_cmd\_strobe lines represent the Brcst[7..2] and BrcstStr1 outputs of the TTCrx respectively. The ccb\_data[7..0] and ccb\_data\_strobe lines represent the data[7..0] and data\_strobe outputs of the TTCrx respectively. Peripheral EMU electronics may need to decode both broadcast (all crates in a system) and individual (only one crate in a system) commands. The same decoding scheme (Table 7) is being used on both fast control and data buses. Subadd[7..0] lines are not provided the peripheral backplane. Note that after power up several outputs of TTCrx, including Dout[7..0], DQ[3..0], SubAdd[7..0] and DoutStr are disabled (chapter 3 of [3]). In order to enable them, bit 5 in the control register of the TTCrx should be set "1".

According to [3], both Clk40Des1 and Clk40Des2 can be used for the synchonization of BrcstStr2 and Brcst[7..6]. The BrcstStr1 and Brcst[5..2] are always synchronized with the Clk40des1. Also there are separate settings for coarse delays for BrcsStr1 and BrcstStr2. So, in order to make a broadcast scheme work in the CCB'2004, the coarse settings for BrcstStr1 and BrcstStr2 should be the same and BrcsStr2 and Brcst[7..6] should be synchronized with the Clk40Des1. This can be done by control access to the TTCrx ASIC. This is a default state after power up and reset.

Several Hard\_Reset commands (from either Brcst[7..2] or Data[7..2] busses) are decoded inside the CCB2004 (they are marked red in Table 7). All other commands must be decoded by targeted peripheral boards from the ccb\_cmd[5..0]+ccb\_cmd\_strobe AND ccb\_data[7..2]+ccb\_data\_strobe lines.

Table 7: Fast Control Bus Ccb cmd[5..0] and Ccb data[7..2] (\*) Commands

| Signal               | Code (hex) | Description                                         |

|----------------------|------------|-----------------------------------------------------|

| BC0                  | 01         | Bunch Crossing Zero                                 |

| OC0                  | 02         | Orbit Counter Reset                                 |

| L1 Reset             | 03         | Reset L1 readout buffers                            |

| Hard_reset (**)      | 04         | Reload all FPGAs from EPROMs                        |

| Start Trigger        | 06         |                                                     |

| Stop Trigger         | 07         |                                                     |

| Test Enable          | 08         |                                                     |

| Private Gap          | 09         |                                                     |

| Private Orbit        | 0A         |                                                     |

| CCB_hard_reset (***) | 0F         | Reload Xilinx FPGA from its EPROM on CCB'2004 board |

| Tmb_hard_reset (**)  | 10         | Reload TMB FPGA's from EPROM                        |

| Alct_hard_reset (**) | 11         | Reload ALCT FPGA's from EPROM                       |

| Dmb_hard_reset (**)  | 12         | Reload DMB FPGA's from EPROM                        |

| Mpc_hard_reset (**)  | 13         | Reload MPC FPGA's from EPROM                        |

| Dmb_cfeb_calibrate0  | 14         | CFEB Calibrate Pre-Amp Gain                         |

| Dmb_cfeb_calibrate1  | 15         | CFEB Trigger Pattern Calibration                    |

| Dmb_cfeb_calibrate2       | 16 | CFEB Pedestal Calibration                                             |  |  |  |  |  |

|---------------------------|----|-----------------------------------------------------------------------|--|--|--|--|--|

| Dmb_cfeb_initiate         | 17 | Initiate CFEB calibration (Hold next L1ACC and Pretriggers)           |  |  |  |  |  |

| Alct_adb_pulse_sync       | 18 | Pulse Anode Discriminator, synchronous                                |  |  |  |  |  |

| Alct_adb_pulse_async      | 19 | Pulse Anode Discriminator, asynchronous                               |  |  |  |  |  |

| Clct_external_trigger     | 1A | External Trigger All CLCTs                                            |  |  |  |  |  |

| Alct_external_trigger     | 1B | External Trigger All ALCTs                                            |  |  |  |  |  |

| Soft_reset                | 1C | Initializes the FPGA on DMB, TMB and MPC boards                       |  |  |  |  |  |

| DMB_soft_reset            | 1D | Initializes the FPGA on a DMB                                         |  |  |  |  |  |

| TMB_soft_reset            | 1E | Initializes the FPGA on a TMB                                         |  |  |  |  |  |

| MPC_soft_reset            | 1F | Initializes the FPGA on a MPC                                         |  |  |  |  |  |

| Inject patterns from TMBs | 24 | Inject test patterns from the TMB's internal RAM to MPC               |  |  |  |  |  |

| Alct_adb_pulse            | 25 | Generate both synchronous and asynchronous anode discriminator pulses |  |  |  |  |  |

| Inject patterns from SP   | 2F | Inject test patterns from the SP's internal FIFO to MS                |  |  |  |  |  |

| Inject patterns from MPC  | 30 | Inject test patterns from the MPC's internal FIFO to SP               |  |  |  |  |  |

| Inject patterns from MS   | 31 | Inject test patterns from the MS's internal FIFO to GMT               |  |  |  |  |  |

| Bunch Counter Reset       | 32 | Resets bunch counters                                                 |  |  |  |  |  |

<sup>(\*)</sup> – data[1..0] can be any values

### 3.3. L1ACC and Pretrigger Sources and Control

There are ten possible sources for L1ACC and two Pretriggers (ALCT\_external\_trigger and CLCT\_external\_trigger) in "FPGA" mode:

- TTCrx\_L1ACC (25 ns pulse),

- External L1ACC (LVDS input coming through the front panel),

- Tmb\_l1a\_request (25 ns pulse coming over custom backplane),

- Tmb\_l1a\_release (25 ns pulse coming over custom backplane)

- Artificial L1ACC generated upon VME write to (base + 54) address (see Table 8),

- Any source of ALCT\_adb\_pulse\_sync (VME, TTC command),

- Any source of ALCT\_adb\_pulse\_async (VME, TTC command)

- DMB\_cfeb\_calibrate[2..0] pulses (VME, TTC command); logical "OR" of three pulses.

Each of these sources can be masked using dedicated CSRB1 bits (disabled if "1" and enabled if "0"). Before distribution to backplane both Pretriggers can be delayed for a number of 40Mhz clocks (from 1 to 255, defined by CSRB5[15..8]). Independently from Pretriggers, the L1ACC can also be delayed for n=1..255 clock cycles where (n) is defined by CSRB5[7..0]. The ALCT\_adb\_pulse\_sync and ALCT\_adb\_pulse\_async backplane signals are sent to backplane without delay. These sources may produce L1ACC to backplane when CSRA1[0]=0 independently from CSRB1[0]. In "discrete logic" mode, when the CSRA1[0]=1, only L1ACC from TTCrx may unconditionally propagate to custom backplane with a delay of ~50 ns.

There is a 32-bit counter of L1ACC requests. The counter counts the L1ACC requests from any selected source in the FPGA even if the transmission to backplane is disabled. The counter is disabled after power up and the CCB2004 internal reset.

<sup>(\*\*) –</sup> decoded by CCB

<sup>(\*\*\*) -</sup>decoded only by discrete logic interface of the CCB from the TTCrq outputs

In a special CFEB calibration mode, the CCB2004 may receive a dmb\_cfeb\_initiate command from the TTCrx (this command can be also send upon write to a specific VME address, see Table 8). In this mode, the CCB2004 "holds" the next L1ACC and both Pretriggers (by preventing them from being broadcast on the backplane). In a similar way, if the CSRB1[13]=1, then the CCB2004 holds the next L1ACC and Pretriggers after the first L1ACC has been sent to backplane. The CCB'2004 can exit from this "hold" mode when a dmb\_l1a\_release or tmb\_l1a\_release signals have been received from DMB or TMB or when VME write to (base address + 58) has been performed.

#### 3.4. Reloading Signals

The Xilinx FPGA residing on CCB2004 board can be reloaded from its EPROM on common and CCB-specific "Hard\_reset" commands (Table 7) if switch S10-8 is "on" (see Section 7). Reconfiguration time is ~60 ms. Note that when common "Hard\_Reset" or "CCB\_Hard\_reset" commands are decoded inside the FPGA, they in fact do not force reconfiguration of the FPGA itself. These commands are effective for FPGA reconfiguration only after decoding by discrete logic.

Hard\_reset reloading signals (from either Brcst[7..2] or Data[7..2] busses) are decoded by the CCB2004 and expanded to 500 ns before distribution to the backplane. There is also a common Hard\_reset command (Table 7), that causes generation of all reloading signals to all boards in a crate simultaneously.

An ALCT, TMB, DMB and MPC cards inform the CCB2004 when they have completed the reconfiguration process by asserting their cfg\_done signals. These static signals are available for reading from CSRA2-3 (see 3.2-3.3).

### 4. VME Interface and Control and Status Registers (CSR)

The CCB2004 can be accessed in the VME crate using geographical addressing that utilizes the address pins GA<4-0> available on the VME64x backplane. In this mode the CCB2004 recognizes its address space when the code on address lines A<23-19> is equal to the 5-bit geographical code of its slot. The base address is 600000(hex) in the Track Finder crate (slot 12) and 680000(hex) in the peripheral crate (slot 13). The board recognizes an AM codes 39(hex), 3D(hex) and supports A24D16 slave operations. The CCB2004 does not respond to byte-addressing modes, so all valid addresses must be even numbers. The list of available VME addresses is given in Table 8.

There are two groups of Control and Status Registers (CSR): CSRA and CSRB. The group A is implemented in a discrete logic and the group B in Xilinx FPGA.

Table 8

| Address (hex) | Address (hex) Function                                                       |  |  |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|               | Group A, discrete logic                                                      |  |  |  |  |  |  |  |

| Base + 0      | CSRA1 (control/status register), discrete logic                              |  |  |  |  |  |  |  |

| Base + 2      | CSRA2 (status register), discrete logic. Write to CSRA2 causes generation of |  |  |  |  |  |  |  |

|                     | Hard reset for the FPGA. See 4.2. for more details.                                                             |

|---------------------|-----------------------------------------------------------------------------------------------------------------|

| Base + 4            | CSRA3 (status register), discrete logic. Write to CSRA3 causes generation of Soft reset                         |

|                     | for the FPGA See 4.3. for more details.                                                                         |

|                     |                                                                                                                 |

|                     | Group B, FPGA                                                                                                   |

| Base + 20           | CSRB1 (control register), FPGA                                                                                  |

| Base + 22           | CSRB2 (command bus), FPGA                                                                                       |

| Base + 24           | CSRB3 (data bus), FPGA                                                                                          |

| Base + 26           | CSRB4 (general purpose R/W register, future use), FPGA                                                          |

| Base + 28           | CSRB5 (delay register), FPGA                                                                                    |

| Base + 2a           | CSRB6 (control register), FPGA                                                                                  |

| Base + 2c           | CSRB7 (QPLL control register), FPGA                                                                             |

| Base + 2e           | CSRB8 (general purpose R/W register, future use), FPGA                                                          |

| Base + 30           | CSRB9 (status register, serial ID chip), FPGA                                                                   |

| Base + 32           | CSRB10, not implemented, FPGA                                                                                   |

| Base + 34           | CSRB11 (status register), FPGA                                                                                  |

| Base + 36           | CSRB12 (status register), FPGA                                                                                  |

| Base + 38           | CSRB13 (status register), FPGA                                                                                  |

| Base + 3a           | CSRB14 (status register), FPGA                                                                                  |

| Base + 3c           | CSRB15 (status register), FPGA                                                                                  |

| Base + 3e           | CSRB16 (status register), FPGA                                                                                  |

| Base + 40           | CSRB17 (status register, date of firmware revision), FPGA                                                       |

| Base + 42           | CSRB18 (TTCrx hardwired ID number). Read only. Valid after TTCrx reset.                                         |

| D + 44              | CSRB18[70] = Data[70] and $CSRB18[158] = SubAdr[70]$                                                            |

| Base + 44           |                                                                                                                 |

| Base + 46 Base + 48 |                                                                                                                 |

| Base + 4a           |                                                                                                                 |

| Base + 4c           |                                                                                                                 |

| Base + 4e           |                                                                                                                 |

| Base + 50           | Generate L1Reset 25 ns pulse (write only), FPGA (*)                                                             |

| Base + 52           | Generate BC0 25 ns pulse (write only), FPGA (*)                                                                 |

| Base + 54           | Generate L1ACC 25 ns pulse (write only) and external triggers (if enabled), FPGA (*)                            |

| Base + 56           | Generate "DMB cfeb initiate" pulse (write only) to hold the next L1ACC and                                      |

|                     | Pretriggers, FPGA                                                                                               |

| Base + 58           | Generate "Release HOLD L1ACC Mode" pulse to enable transmission of the L1ACC and Pretriggers (write only), FPGA |

| Base + 5a           | Reset CSRB11 Error Bits (write only), FPGA                                                                      |

| Base + 5c           | Reset TTCrx ASIC (write only). Generates 50 us pulse of negative polarity to TTCrx.                             |

| Base + 5e           |                                                                                                                 |

| Base + 60           | Generate "Hard_Reset" 500 ns pulse to all modules in the crate (write only), FPGA (*)                           |

| Base + 62           | Generate "TMB_Hard_Reset" 500 ns pulse to all TMB boards in the crate (write only), FPGA (*)                    |

| Base + 64           | Generate "DMB_Hard_Reset" 500 ns pulse to all DMB boards in the crate (write only), FPGA (*)                    |

| Base + 66           | Generate "ALCT_Hard_Reset" 500 ns pulse to all ALCT boards (write only), FPGA (*)                               |

| Base + 68           | Generate "MPC_Hard_Reset" 500 ns pulse to MPC (write only), FPGA (*)                                            |

| Base + 6a           | Generate "Soft_Reset" 25 ns pulse to TMB, DMB, MPC boards in the crate (write only), FPGA (*)                   |

| Base + 6c           | Generate "TMB_Soft_Reset" 25 ns pulse to TMB boards (write only), FPGA (*)                                      |

| Base + 6e           | Generate "DMB_Soft_Reset" 25 ns pulse to TMB boards (write only), FPGA (*)                                      |

| Base + 70           | Generate "MPC_Soft_Reset" 25 ns pulse to TMB boards (write only), FPGA (*)                                      |

| Base + 72           | • • • • • • • • • • • • • • • • • • • •                                                                         |

| Base + 74 |                                                                                            |

|-----------|--------------------------------------------------------------------------------------------|

| Base + 76 |                                                                                            |

| Base + 78 |                                                                                            |

| Base + 7a |                                                                                            |

| Base + 7c |                                                                                            |

| Base + 7e |                                                                                            |

| Base + 80 | Congrete both "ALCT odb pulse gyme" and "ALCT odb pulse agyme" (yyrite only)               |

| Dase + 80 | Generate both "ALCT_adb_pulse_sync" and "ALCT_adb_pulse_async" (write only), FPGA (*)      |

| Base + 82 | Generate "ALCT_adb_pulse_sync" 500 ns pulse (write only), FPGA (*)                         |

| Base + 84 | Generate "ALCT_adb_pulse_async" pulse (write only), FPGA (*)                               |

| Base + 86 | Generate "CLCT_external_trigger" 25 ns pulse (write only), FPGA (*)                        |

| Base + 88 | Generate "ALCT_external_trigger" 25 ns pulse (write only), FPGA (*)                        |

| Base + 8a | Generate "DMB_cfeb_calibrate[0]" 25 ns pulse (write only), FPGA (*)                        |

| Base + 8c | Generate "DMB_cfeb_calibrate[1]" 25 ns pulse (write only), FPGA (*)                        |

| Base + 8e | Generate "DMB_cfeb_calibrate[2]" 25 ns pulse (write only), FPGA (*)                        |

| Base + 90 | Read L1ACC Counter[150] (read only), FPGA                                                  |

| Base + 92 | Read L1ACC Counter[3116] (read only), FPGA                                                 |

| Base + 94 | Reset L1ACC Counter to 0 (write only), FPGA                                                |

| Base + 96 | Enable L1ACC Counter to count (write only), FPGA                                           |

| Base + 98 | Disable L1ACC Counter to count (write only), FPGA                                          |

| Base + 9a | Generate 800 us "Reset pulse" on 1-Wire bus to initialize the serial ID chip (write only), |

|           | FPGA                                                                                       |

| Base + 9c | Generate 3 us "Read pulse" on 1-Wire bus to read data from the serial ID chip (write       |

|           | only), FPGA                                                                                |

| Base + 9e | Reset CSRB9 (write only), FPGA                                                             |

| Base + a0 | Generate "Write-zero" 50 us pulse on 1-Wire bus to send a command to serial ID chip        |

|           | (write only), FPGA                                                                         |

| Base + a2 | Generate "Write-one" 12 us pulse on 1-Wire bus to send a command to serial ID chip         |

|           | (write only), FPGA                                                                         |

| (*) Tl    | Lyrita commands cause generation of pulses of specific length ante dedicated backplane     |

<sup>(\*)</sup> These optional write commands cause generation of pulses of specific length onto dedicated backplane lines. Ccb\_cmd[5..0], ccb\_cmd\_strobe, ccb\_data[7..0], ccb\_data\_strobe lines remain inactive during these commands. These commands are independent from CSRB1[0].

# 4.1. CSRA1 (base + 00)

| T.1 | 4.1. CSKAI (base + 00) |                                                                                          |  |

|-----|------------------------|------------------------------------------------------------------------------------------|--|

| Bit | Access                 | Function                                                                                 |  |

| 0   | R/W                    | Source of signals to custom backplane (FPGA if "0" and discrete logic interface if "1"). |  |

| 1   | R/W                    | Enable Read operations over I2C bus from TTCrx ASIC (active "0")                         |  |

| 2   | R/W                    | I2C_SDA line (active "0")                                                                |  |

| 3   | R/W                    | I2C_SCL line (active "0")                                                                |  |

| 4   | R                      | I2C_SDA line (read only)                                                                 |  |

| 5   | R/W                    | FPGA_TDI pin of the JTAG interface to FPGA/EPROM                                         |  |

| 6   | R/W                    | FPGA_TMS pin of the JTAG interface to FPGA/EPROM                                         |  |

| 7   | R/W                    | FPGA_TCK pin of the JTAG interface to FPGA/EPROM                                         |  |

| 8   | R                      | FPGA_TDO pin of the JTAG interface from FPGA/EPROM (read only)                           |  |

| 9   | R/W                    | -                                                                                        |  |

| 10  | R/W                    | -                                                                                        |  |

| 11  | R/W                    | -                                                                                        |  |

| 12  | R/W                    | -                                                                                        |  |

| 13  | R/W                    | -                                                                                        |  |

| 14  | R/W                    | -                                                                                        |  |

| 15  | R/W                    | -                                                                                        |  |

# 4.2. CSRA2 (base + 02)

Write operation to CSRA2 (any data) causes unconditional "Hard Reset" of the FPGA. Data format for read operations is shown in a table below.

| Bit | Access | Function                                                                                  |

|-----|--------|-------------------------------------------------------------------------------------------|

| 0   | R      | Mpc_cfg_done (peripheral crate) (active "0") or MS_cfg_done (TF crate) (active "0")       |

| 1   | R      | Alct_cfg_done_1 (peripheral crate) (active "0")                                           |

| 2   | R      | Alct_cfg_done_2 (peripheral crate) (active "0")                                           |

| 3   | R      | Alct_cfg_done_3 (peripheral crate) (active "0")                                           |

| 4   | R      | Alct_cfg_done_4 (peripheral crate) (active "0") or SP_cfg_done_3 (TF crate) (active "0")  |

| 5   | R      | Alct_cfg_done_5 (peripheral crate) (active "0") or SP_cfg_done_6 (TF crate) (active "0")  |

| 6   | R      | Alct_cfg_done_6 (peripheral crate) (active "0") or SP_cfg_done_7 (TF crate) (active "0")  |

| 7   | R      | Alct_cfg_done_7 (peripheral crate) (active "0")                                           |

| 8   | R      | Alct_cfg_done_8 (peripheral crate) (active "0") or SP_cfg_done_10 (TF crate) (active "0") |

| 9   | R      | Alct_cfg_done_9 (peripheral crate) (active "0")                                           |

| 10  | R      | Tmb_cfg_done_1 (peripheral crate) (active "0")                                            |

| 11  | R      | Tmb_cfg_done_2 (peripheral crate) (active "0")                                            |

| 12  | R      | Tmb_cfg_done_3 (peripheral crate) (active "0")                                            |

| 13  | R      | Tmb_cfg_done_4 (peripheral crate) (active "0") or SP_cfg_done_2 (TF crate) (active "0")   |

| 14  | R      | Tmb_cfg_done_5 (peripheral crate) (active "0") or SP_cfg_done_5 (TF crate) (active "0")   |

| 15  | R      | Tmb_cfg_done_6 (peripheral crate) (active "0")                                            |

### 4.3. CSRA3 (base + 04)

Write operation to CSRA3 (any data) causes "Soft Reset" of the FPGA logic, including reset of CSRB11[10..8], reset of L1ACC counter, disable L1ACC counter, enable unconditional propagation of L1ACC from selected source(s) to custom backplane. Data format for read operations is shown in a table below.

| Bit | Access | Function                                                                                 |

|-----|--------|------------------------------------------------------------------------------------------|

| 0   | R      | Tmb_cfg_done_7 (peripheral crate) (active "0") or SP_cfg_done_8 (TF crate) (active "0")  |